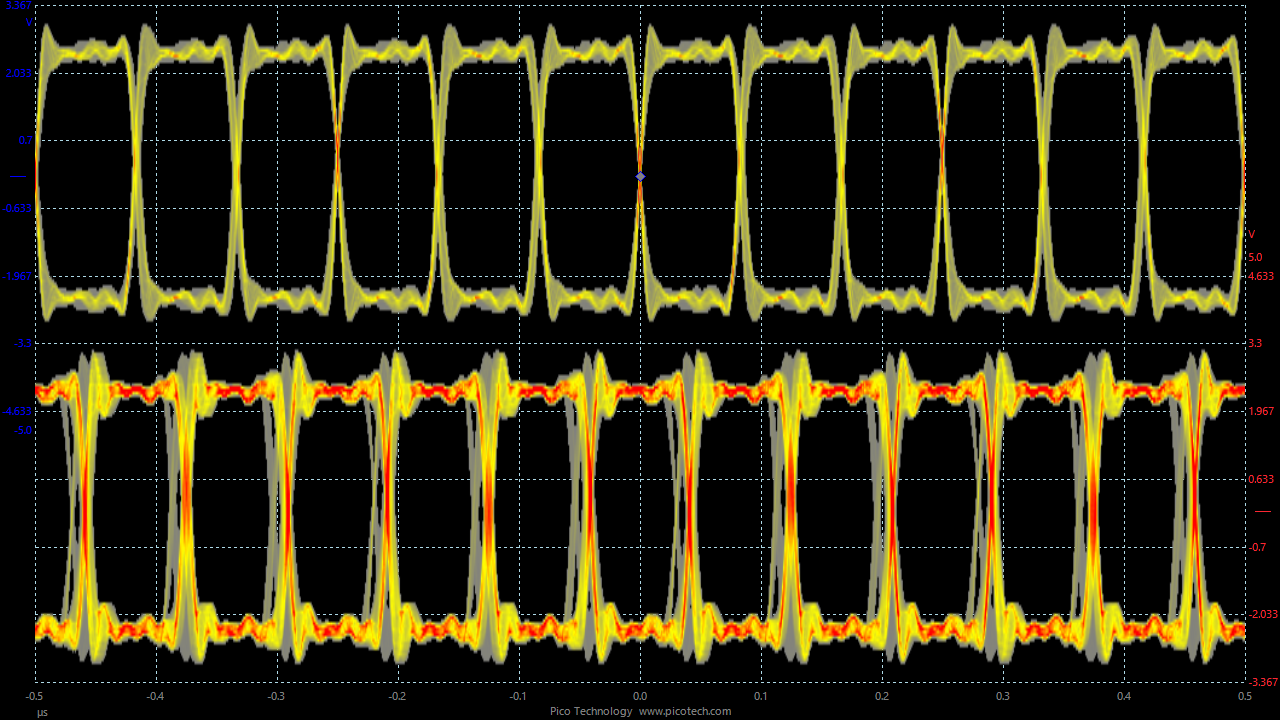

My favorite phenomenon in digital circuitry is when digital threatens to become analog again. For example, a lot of people are interested in the idea of overclocking an FPGA for more performance and are usually encouraged not to do so. However, thinking about the reasons why overclocking goes wrong and learning to understand the issues with overclocking can allow you to achieve a stable overclock or at least help you understand your chip better. This is only one example of exploring odd behavior of FPGAs when pushing beyond suggested limits.

Every sensor is a temperature sensor, nearly everything is a resistor or a conductor if you try hard enough and anything is an antenna. Datasheets are just a suggestion, and finally, often we pretend things are ideal, when they often are not.

Continue reading Unconventional uses of FPGAs